# SACLANT ASW RESEARCH CENTRE

SACLANTCEN

Conference Proceedings No. 25

PART 1 SESSIONS I to III

# SACLANT ASW RESEARCH CENTRE

# REAL-TIME GENERAL-PURPOSE, HIGH-SPEED SIGNAL PROCESSING SYSTEMS FOR UNDERWATER RESEARCH

Proceedings of a Working Level Conference held at SACLANTCEN on 18-21 September 1979

Organized by

ROBERT SEYNAEVE

1 DECEMBER 1979

NORTH

ATLANTIC

TREATY

ORGANIZATION

LA SPEZIA, ITALY

This document is unclassified. The information it contains is published subject to the conditions of the legend printed on the inside cover. Short quotations from it may be made in other publications if credit is given to the author(s). Except for working copies for research purposes or for use in official NATO publications, reproduction requires the authorization of the Director of SACLANTCEN.

This document is released to a NATO Government at the direction of the SACLANTCEN subject to the following conditions:

- 1. The recipient NATO Government agrees to use its best endeavours to ensure that the information herein disclosed, whether or not it bears a security classification, is not dealt with in any manner (a) contrary to the intent of the provisions of the Charter of the Centre, or (b) prejudicial to the rights of the owner thereof to obtain patent, copyright, or other like statutory protection therefor.

- 2. If the technical information was originally released to the Centre by a NATO Government subject to restrictions clearly marked on this document the recipient NATO Government agrees to use its best endeavours to abide by the terms of the restrictions so imposed by the releasing Government.

Compiled and Published by

# SACLANTCEN CONFERENCE PROCEEDINGS No. 25

#### NORTH ATLANTIC TREATY ORGANIZATION

SACLANT ASW Research Centre Viale San Bartolomeo 400, I-19026 San Bartolomeo (SP), Italy.

tel:  $\frac{\text{national}}{\text{international} + 39} \frac{0187}{187} \frac{503540}{503540}$

telex: 271148 SACENT I

REAL-TIME, GENERAL-PURPOSE, HIGH-SPEED SIGNAL PROCESSING SYSTEMS

FOR UNDERWATER RESEARCH

Proceedings of a Working Level Conference held at SACLANTCEN on 18-21 September 1979

(Part 1: SESSIONS I to III)

Organized by ROBERT SEYNAEVE

1 December 1979

This document has been prepared from text and illustrations provided by each author. The opinions expressed are those of the authors and are not necessarily those of the SACLANT ASW Research Centre.

# LIST OF PARTICIPANTS

# CANADA

Mr D.V. Crowe

Defence Research Establishment

P.O. Box 1012

Dartmouth

Nova Scotia B2Y 3Z7

#### DENMARK

Mr B. Damsgaard Danish Defence Research Establishment Staunings Plads 2 DK 2100 Copenhagen  $\emptyset$

Mr. P.B. Ring

Danish Defence Research Establishment

Staunings Plads 2

DK 2100 Copenhagen Ø

#### FRANCE

Mr J.L. Lambla GERDSM D.C.A.N Toulon 83800 Toulon Naval

Mr J.Maigre GERDSM D.C.A.N. Toulon 83800 Toulon Naval

#### GERMANY

Dr J.F. Böhme

FGAN-Forschungsinstitut für

Hochfrequenzphysik

Königstrasse 2

D-5307 Wachtberg-Werthhoven

Mr H. Herwig Forschungsanstalt der Bundeswehr für Wasserschall und Geophysik Klausdorfer Weg 2-24 2300 Kiel

Ing. Kh. Rosenback

FGAN-Forschungsinstitut für

Hochfrequenzphysik

Königstrasse 2

D-5307 Wachtberg-Werthhoven

# GERMANY (Cont.)

Mr B. Scholz

Forschungsanstalt der Bundeswehr für

Wasserschall und Geophysik

Klausdorfer Weg 2-24

2300 Kiel

Dipl.Ing. H. Urban Fried. Krupp GMBH Krupp Atlas-Elektronik Postfach 44 85 45 2800 Bremen 44

Dipl.Ing. W. Wagner Fried. Krupp GMBH Krupp Atlas-Elektronik Postfach 44 85 45 2800 Bremen 44

# ITALY

Prof V. Cappellini Istituto di Elettronica Universita di Firenze Via di S. Marta 3 50139 Firenze

C.C.(AN) D. Nascetti,IN

Marina Militare

Commissione Permanente per gli Esperimenti

del Materiale da Guerra

La Spezia 19026

T.V.(AN) G.C. Testino, IN

Marina Militare

Commissione Permanente per gli Esperimenti

del Materiale da Guerra

La Spezia 19026

#### NETHERLANDS

Mr J.G. Schothorst Physics Laboratory TNO Oude Waalsdorperweg 63 Post Box 96864 2509 JG Den Haag

Mr C.H. Vlasblom Physics Laboratory TNO Oude Waalsdorperweg 63 Post Box 96864 2509 JG Den Haag

# NORWAY

Dr H.J. Alker Electronics Research Laboratory O.S. Bragstads Plass 4 N-7034 Trondheim-Nth

Mr K. Hansen SIMRAD A/S P.O. Box 111 Horten

Dr. Y.C. Lundh Norwegian Defence Research Establish-Postboks 25 N-2007 Kjeller

Dr G.B. Pettersen

Norwegian Defence Research EstablishPostboks 115

N-3191 Horten

# UNITED KINGDOM

Dr J.C. Cook

Admiralty Marine Technology

Queens Road

Teddington, Middlesex

Dr T.E. Curtis

Admiralty Underwater Weapons

H.M. Naval Base

Portland, Dorset

Prof J.W.R. Griffiths

Department of Electronic & Electrical

University of Technology

Loughborough

Leicestershire, LE11 3TU

Mr S.F. Meatcher

Admiralty Underwater Weapons

H.M. Naval Base

Portland, Dorset

Dr D. Nairn

Admiralty Underwater Weapons

H.M. Naval Base

Portland, Dorset

Dr J.S. Pyett

Admiralty Underwater Weapons

H.M. Naval Base

Portland, Dorset

# UNITED KINGDOM (Cont.)

Mr C. Richardson

Admiralty Underwater Weapons

H,M, Naval Base

Portland, Dorset

Mr T. Totten Royal Aircraft Establishment Farnborough, Hants

# UNITED STATES

Prof A.B. Baggeroer

Massachusetts Institute of Technology

Department of Ocean Engineering

Cambridge

Mass. 02139

Mr J.M. Griffin Naval Research Laboratory Code 8160 4555 Overlook Avenue SW Washington D.C. 20375

Mr E. Hug Naval Underwater Systems Center New London, Connecticut 06320

Mr F.W. Molino Naval Underwater Systems Center New London, Connecticut 06320

Dr B.L. Pennoyer Naval Ocean Systems Center San Diego, California 92152

CAPT C.M. Rigsbee. USN

Assistant Commander for Research &

Naval Air Systems Command

Department of the Navy

Washington D.C. 20360

Mr P.A. Rigsbee Naval Research Laboratory Code 7594 Washington D.C. 20375

Mr D. Steiger Naval Research Laboatory Code 8003 Washington D.C. 20375

Mr J.E. Vernaglia Naval Underwater Systems Center New London, Connecticut 06320

# UNITED STATES (Cont.)

Mr S. Weinstein Naval Research Laboratory Code 7593 Washington D.C. 20375

Mr Y.S. Wu Naval Research Laboratory Code 7590 Washington D.C. 20375

# SACLANT HQ

CAPT A. Newing, UKN (Rtd)

# SACLANTCEN

Mr P. Boni

Mr E. Cernich

Mr V. Duarte

Mr F. Jensen

Mr.W. Kupermann

Mr C. Maloberti

Mr M. McCann

Mr P. Nesfield

Mr G. Orsini

Mr R. Seynaeve

Mr G.C. Vettori

Other members of SACLANTCEN staff also participated,

# TABLE OF CONTENTS

|                                                                                  | PART 1 - SESSIONS I to III                               |     | Page         |

|----------------------------------------------------------------------------------|----------------------------------------------------------|-----|--------------|

| INTRODUCTION                                                                     |                                                          |     | 1            |

| SESSION I SYSTEMS                                                                |                                                          |     |              |

| A general purpose software<br>different fields of physic<br>by Poul B. Ring      | system for applications in s                             | (a) | 1-1 to 1-9   |

|                                                                                  | ing system for producing the ribution of acoustic energy | (b) | 2-1 to 2-11  |

| SACLANTCEN real-time signa<br>by Robert Seynave et al                            | al processing system                                     | (c) | 3-1 to 3-20  |

| NOSC signal processing eva<br>by Bryson Pennoyer                                 | luation laboratory                                       | (d) | 4-1 to 4-9   |

| Using intelligent graphics processing Daniel Steiger                             | terminals in real-time                                   | (e) | 5-1 to 5-9   |

| The application of high-sp experiments using explosive by J.S. Pyett             | eed processors to propagation<br>wes                     | (f) | 6-1 to 6-5   |

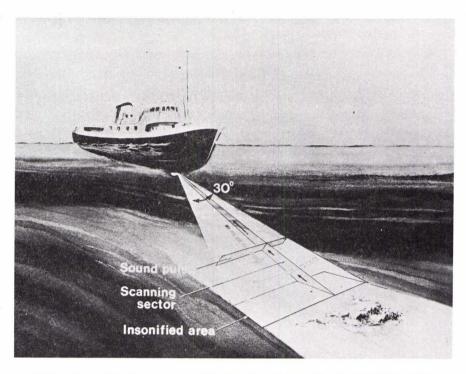

| Digital signal processing pulse sector scanning sona by J.C. Cook & A. Rushworth | rs                                                       | (g) | 7-1 to 7-17  |

| Panel on General Purpos                                                          | e Systems and Future Trends                              |     | I-1 to I-4   |

| SESSION II PROCESSORS                                                            |                                                          |     |              |

| A micro-programmable corre<br>processing<br>by Hans-Jørgen Alker                 | lator for real-time radar                                | (h) | 8-1 to 8-6   |

| MARTINUS - Multiprocessor<br>processing<br>by Yngvar Lundh                       | for high capacity real-time                              | (i) | 9-1 to 9-8   |

| A modular approach to sign by T.E. Curtis                                        | al processing                                            | (j) | 10-1 to 10-8 |

| Table of Contents (Cont'd)                                                                                                 |     | Page           |

|----------------------------------------------------------------------------------------------------------------------------|-----|----------------|

| Development of military ARGUS computers and MOD bus for<br>close-coupled signal processing applications<br>by Donald Nairn | (k) | 11-1 to 11-9   |

| The AP-120B array processor<br>by Walter Wagner                                                                            | (1) | 12-1 to 12-4   |

| The MPS-3 and the SPS-81 by John S. Padgett (presented by J.M. Griffin)                                                    | (m) | 13-1 to 13-5   |

| Experience with a MAP 300 array processor by P. Nesfield                                                                   | (n) | 14-1 to 14-8   |

| Advanced digital processor research at DREA (Informal Presentation) by D.V. Crowe                                          | (0) | 15-1 to 15-2   |

| Overview of the ADPS signal processor<br>(Informal Presentation)<br>by Bryson Pennoyer                                     | (p) | 16-1           |

| MAP 300/AP 120B comparison<br>(Informal Presentation)<br>by H.J. Alker                                                     | (q) | 17-1           |

| Panel on Processors                                                                                                        |     | II-1 to II-6   |

| SESSION III DISPLAYS                                                                                                       |     |                |

| Graphics for real-time signal processing systems by M.J. McCann                                                            | (r) | 18-1 to 18-14  |

| Display techniques<br>by S.F. Meatcher                                                                                     | (s) | 19-1 to 19-14  |

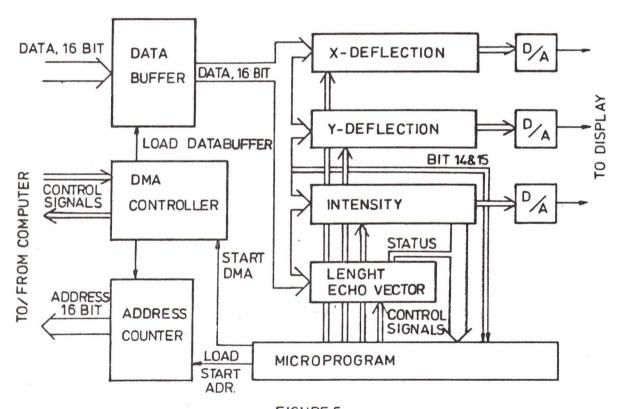

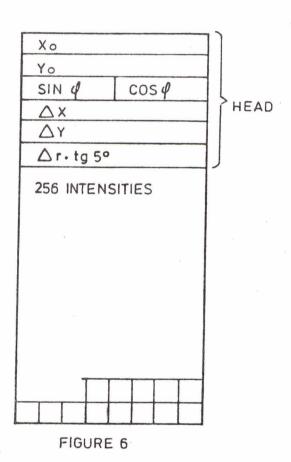

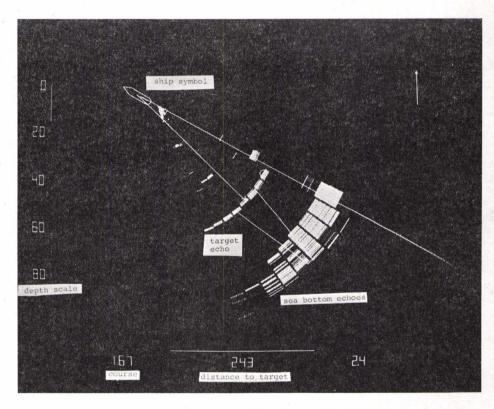

| A fast display processor for sonar echoes<br>by Helge Bodholt                                                              | (t) | 20-1 to 20-7   |

| Panel on Displays                                                                                                          |     | III-1 to III-4 |

| PART 2 - SESSIONS IV to VI                                                                                                 |     |                |

| SESSION IV SOFTWARE                                                                                                        |     |                |

| User orientated software for signal analysis by C. Richardson                                                              | (u) | 21-1 to 21-5   |

| System functional migration - High level language to hardware by Y.S. Wu and G.R. Lloyd                                    | (v) | 22-1 to 22-9   |

| Table of Contents (Cont'd)                                                                                                    |      | Page          |

|-------------------------------------------------------------------------------------------------------------------------------|------|---------------|

| Signal processing language and operating system by S. Weinstein                                                               | (w)  | 23-1 to 23-12 |

| A modular signal processing software development system by Peter A. Rigsbee                                                   | (x)  | 24-1 to 24-9  |

| Laboratory utilization of a standard signal processor<br>by Frank W. Molino et al                                             | (y)  | 25-1 to 25-13 |

| MASCOT - A modular software construction system (Informal Presentation) by Donald Nairn                                       | (z)  | 26-1 to 26-5  |

| Panel on Software                                                                                                             |      | IV-1 to IV-4  |

| SESSION V BEAMFORMING                                                                                                         |      |               |

| Real-time expanded-band beamforming using a complex<br>heterodyner and fast array processor<br>by D. Vance Crowe              | (aa) | 27-1 to 27-13 |

| Sonar beam-forming with an array processor in real time by Walter G. Wagner                                                   | (bb) | 28-1 to 28-14 |

| An introduction to adaptive array processing by J.W.R. Griffiths                                                              | (cc) | 29-1 to 29-11 |

| Panel on Beamforming                                                                                                          |      | V-1 to V-4    |

| SESSION VI APPLICATIONS                                                                                                       |      |               |

| High-speed simulation of an underwater acoustic field using an array processor by W.A. Kuperman, F.B. Jensen, M.G. Martinelli | (dd) | 30-1 to 30-7  |

| Some high efficiency digital signal processing techniques for high-speed signal processing systems by Vito Cappellini         | (ee) | 31-1 to 31-10 |

| Arrays and array processors - Future real time applications in oceanography and sonar by Arthur B. Baggeroer                  | (ff) | 32-1 to 32-12 |

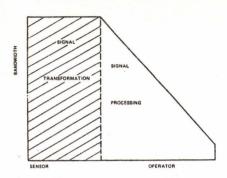

#### INTRODUCTION

During the last few years, advances in the computer field have reached a level where it is possible to implement fast signal-processing systems through the use of standard computer equipment operating in association with more specialized devices, such as high-speed array processors and programmable beamformers. As it appears that in underwater acoustics many different signal processing requirements may be met by the use of sets of common hardware and software functional modules, a general-purpose, on-line, signal-processing facility designed to meet the combined needs of a number of underwater research project will often be the most appropriate approach towards making use of present technology. This can provide important savings in capital outlay and manpower, improve operations, and increase response capability. The purpose of the Conference was for specialists in the subject field to present their views and experiences in the designing of such general-purpose systems. The Conference was also open to other computer and signal-processing specialists who have a working interest in such systems.

Robert Seynaeve Chairman

# <u>ACKNOWLEDGEMENTS</u>

The following SACLANTCEN members made particular contributions to the organization of this Conference:

Mrs June Waller

All the administrative work to prepare the Conference and the Proceedings.

Mr P. Nesfield and Mr M. McCann

The reporting of questions and answers, and of panel discussions.

Messrs V. Duarte, P. Boni and C. Maloberti

Various aspects of the Conference logistics.

NOTE: For the record it is pointed out that the discussions and panels printed herein have not been edited or even read by some of the persons being quoted — this is particularly true for the Panel on General Purpose Systems and Future Trends held on the last day of the Conference.

SESSION I SYSTEMS

# A GENERAL PURPOSE SOFTWARE SYSTEM FOR APPLICATIONS IN DIFFERENT FIELDS OF PHYSICS

by

Poul B. Ring

Danish Defence Research Establishment

Copenhagen, Denmark

ABSTRACT The paper presents the principle of a software system (FTSS) developed by the Danish Defence Research Establishment (DDRE) for applications in different fields of physics. Software is made up by independent modules exchanging data by standarized disc files. Special attention is paid to the production methods of new modules of the extensible system. Since the basic structure of all modules is the same a schedule for production of new modules can be established. Finally as an example an implementation of a ray-trace model is briefly described.

# INTRODUCTION

The paper presents the principle of a software system (FTSS) developed by the Danish Defence Research Establishment (DDRE). The system has been in use since 1973.

The purpose was to make a standarized software system for a number of user groups working in different fields of physics. The intention was that common problems should be solved by a basic package of common software modules, but it should further be possible for the groups to make their own dedicated extensions. Furthermore the system had to be easy to extend for new demands.

These requirements led to the design of a software system with independent modules exchanging data by standardized disc files. Each module performs a specific task and new modules are added to the system depending on new demands. The system is interactive, but batch-facilities are also included.

For the time being (Aug. 1979) the system consists of about 100 modules in fields such as: Timeseries acquisition and analysis, simulation of differential equations, image processing, pattern recognition and a number of simulation models such as sound propagation models, sensor simulations etc.

The system is implemented on a HP-2100 computer using the monitor DOS-III. At present the system is implemented in the environment of the RTE-IV monitor. The software is implemented in Fortran IV.

# 1. FILE STRUCTURE

Data are stored in about ten types of standarized disc files, e.g. timeseries, spectrum, histogram, digital filter, image and record files. The last type of a file represents different types of tables of complex structures. These files are suited to simulation models.

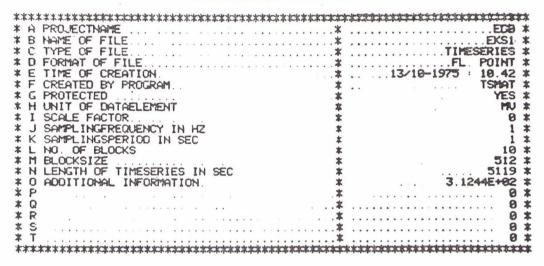

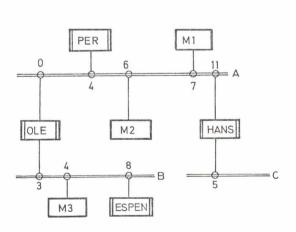

The overall structure of the files is a division in a descriptor and a data section (See fig. 1). A descriptor contains information, name of module which created the file etc. An example of a descriptor for a timeseries file is shown on fig. 2.

# 2. STRUCTURE OF PROGRAMS

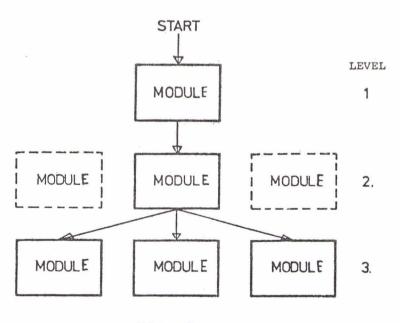

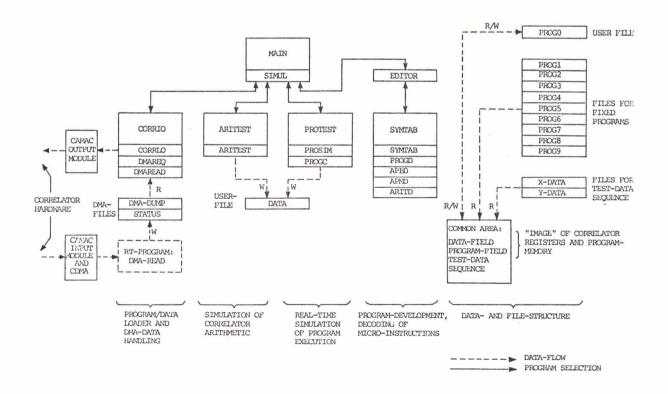

Software is divided into modules placed on three levels. (See fig. 3). The only module on level one is named MAIN. It is the only legal entrance and exit to the FTSS system modules. The most important task of MAIN is to initialize a system data area containing information about the state of the system, e.g. execution in interactive or batch mode, bookcounting of accessed files etc.

All processing modules are placed on level two. On level three a display module and an editor module (editing of descriptors) for each type of the FTSS-files are found.

When FTSS is entered by MAIN there is random access between the modules. The significance of the leves is: If you return to a module from a higher numbered level the module will be in the state as when it was left. In other cases a module is initialized when called.

All modules use only FTSS disc files when accessing data on the disc. To each type of file a collection of accessing subroutines is available.

# 3. THE COMMAND SELECTOR CONCEPT

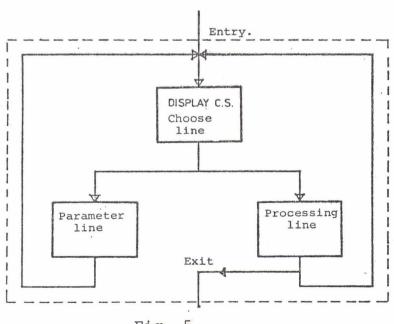

Communication between a user and a module is performed by a command selector, which is a scheme containing a head-line and a number of indexed lines.

The head-line identifies the module. The indexed lines contain values of parameters and processing possibilities. The first step is to select the parameter-lines by typing their index and afterward change or insert the values of the parameters

as desired. Parameters are numbers, text strings or file names. Each time a parameter is changed the terminal is erased and the command-selector is displayed with the new value. (Duration one sec.). Processing of data is performed by typing the index of one of the processing-lines, which are marked by a \*. Examples of command-selectors are shown on fig. 4.

Each module has one and only one command-selector.

# 4. DESIGNING NEW MODULES

Several years experience has shown that the standardization of the communication by means of command-selectors is an advantage for the users of the software because the modules seemes very alike. But also for the designer and programmer the architecture gives advantages.

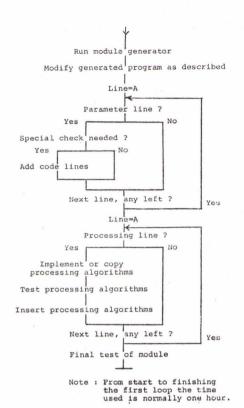

The main reason is that a fixed schedule is used in production of new modules. Following steps are performed.

- Design phase.

- Seperate problem in modules.

- For each module write down the command-selector.

- Design (or copy) processing algorithms.

- Implementation phase.

- Use the module generator program. This is a program having input as a brief description of a command-selector.

Output is a Fortran program containing the communication part of the new module.

- Implement the processing algorithms and merge them (as subroutines) into the generated program.

- Test phase.

- Test each subroutine and repeat the examples for the whole module. (The classical colution).

In the design phase the command selector concept is a convenient tool in the discussions between designers and users having a demand for new software, because a set of command-selectors gives an informative description of user requirements.

In the implementation phase the use of a module generator reduces the production time because Fortran code-lines describing the communication is automatically generated. Another advantage is that the basic structure of all modules is the same (see fig. 5). Therefore a schedule for the implementation phase (see fig. 6) can be used.

In the maintenance phase the similarity of the modules makes it easier to correct a module, esp. in case the module was implemented by a former colleague.

# 5. BATCH

If an analysis is to be performed by many datasets it is clumsy to run the system interactively. Therefore FTSS has been designed to store communication sequences in FTSS batch files. These files can be executed with no interference. A sequence may use several modules and an arbitrary number of FTSS batch files can be stored.

# 6. IMPLEMENTATION OF A RAY-TRACE MODEL

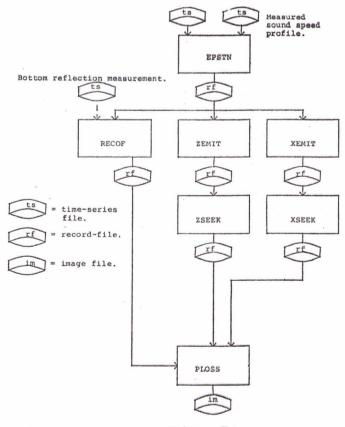

As a dedicated software package an implementation of a raytrace model is briefly described. (See fig. 7). The model consists of 7 independent modules exchanging data by disc files.

The model is based on analytical formulas by a set of functions fitting a measured sound speed profile and a description of bottom and surface by their reflection coefficients.

The modules perform the following tasks :

- Interactive fitting of Epstein profiles to a measured sound speed profile.

- Calculation of reflection coefficients of bottom and surface for a number of selected frequencies.

- By four modules the ray-pattern can be examined in details along a vertical or horizontal line.

- Calculation of the energy distribution of the sound propagation field along a vertical or horizontal line. In case a 2-D display of the energy field is wanted, the calculated energies are stored in an image-file which can be displayed or further processed by the FTSS image package.

The structure of the ray-trace model is typical of models implemented in FTSS, I.e. to split the model components, and let component data be generated by seperate modules and be stored in individual disc files.

# CONCLUSIONS

The principles of a software system with applications in different fields of physics was presented. It is made up by independent modules exchanging data by standarized disc files, which makes the system very easy to extend. All modules have the same basic structure, a standarized communication between user and software and the same schedule is used in production of new modules.

For the user the advantage is a system easy to operate since all modules seems very alike. For the software staff the advantages are a system very excellent to work with in both the production and maintenance phases. After six years experience of working with the system it has proved that structured programming at all levels is very powerfull leading to a fast production of reliable software.

#### REFERENCES

- 1. P.B.Ring, J.K.Nielsen, O.S.Madsen :

A software package for timeseries analysis and acquisition.

(In Danish.) DDRE report 1976/29.

- P.B.Ring, N.O.Jensen :

Digital circuit simulation.

DDRE report 1978/46

- O.C.Mortensen, P.B.Ring:

A software package for fundamental image processing.

DDRE report 1978/42

- 4. A.V.Møller, P.B.Ring, O.C.Mortensen:

A database software package for a multichannel sensor system.

DDRE report 1978/47

- 5. P.B.Ring:

Software packages for description and rendering of geometric objects.

DDRE report 1978/48

- 6. M.Caspersen, P.B.Ring: A simulation model for an infrared sensor in a scenario. DDRE report 1979/27

- 7. H.Preuss, A.Nielsen, M.Andersen:

Description of geometric objects by their contours.

DDRE report 1979/30

- 8. T.Strarup, V.Jeppesen:

A ray-trace sound propagation model.

To be published.

- 9. T.Strarup, A.Pedersen:

A mono pole source array sound propagation model.

To be published.

- 10. G.Hvedstrup Jensen :

A software package for pattern recognition and image

analysis.

To be published.

# DISCUSSION

- T. Totten Aren't disc files slow?

- $\underline{\text{P.B. Ring}}$  It depends very much on the case; in the field of image processing it has been a problem, therefore, we extend the "core" to 256 K.

- $\underline{\text{D. Nairn}}$  How many man-years were required in developing the system?

- $\underline{P.B.}$  Ring Up to now we have invested approximately twenty man-years in modelling and programming the system.

- $\underline{\text{R. Seynaeve}}_{\text{system?}}$  What will be the future evolution of your

- P.B. Ring The next step is to switch from the HP-DOS III monitor to the HP-RTE IV monitor and to add an array processor.

Fig. 1

#

Fig. 2

Fig. 3

####

| - 本本本本本本本本本本本本本本本本本本本本本本本本本本本本本本本本本本本本 | *************                                      |

|----------------------------------------|----------------------------------------------------|

| * A BEAM EMITTING FILE                 | *                                                  |

| * B SOUND-SPEED PROFILE*               | 그 사람들이 물건 하는데 그 사람들이 가는데 얼마나 하는데 얼마나 하는데 그리는데 그래요? |

| * C RECIEUING DISTANCE                 | 9 \$                                               |

| Y D MIMDED OF DECIME TO DE EMPTERS     | 421 *                                              |

| Y E MIMOED HE DEAMS TO BE DICOLOUPED   | 21 *                                               |

| * E PEOMOTOGRATION                     |                                                    |

| * G BEAMWIOTH                          | 30 *                                               |

| * H VERTICAL POSITION OF SOURCE *      | 0 ±                                                |

| * I PLOTMEDIUM *                       | SCDEEN *                                           |

| * J * CALCULATE BEAMS *                | · · · · · · · · · · · · · · · · · · ·              |

| * K * Z-0 PLOT                         | **************************************             |

| * L * DZ-DØ PLOT                       |                                                    |

| * M * 7-T PLOT                         |                                                    |

| * N * HEW MODULE .                     | **************************************             |

| * 0 * RETURN *                         | *                                                  |

| ************************************** | · · · · · · · · · · · · · · · · · · ·              |

#

Fig. 4

Fig. 5

Fig. 6

Fig. 7

A Versatile Signal Processing System for Producing the

Angular and Frequency Distribution of Acoustic Energy in Real Time

by

James M. Griffin NAVAL RESEARCH LABORATORY WASHINGTON, D. C. 20375 USA

ABSTRACT For a number of years the US Naval Research Laboratory (NRL) has been conducting a research program in underwater sound propagation using large aperture hydrophone arrays. This research requires the spectral and angular distributions of the sound field with a variety of bandwidth and throughput rate requirements. As the size of the aperture, in terms of number of hydrophones, increases, the demand on the signal processing equipment increases correspondingly. In addition to this growth in processing needs, the move to at-sea, real-time systems demands high reliability and very high speeds to prevent loss of data.

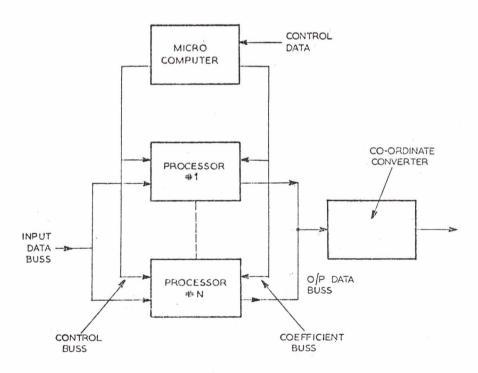

A sea-going signal processing system has been developed at NRL to meet these processing requirements. The system is versatile in that it is composed of a number of small array processors operating in parallel which can be redistributed to handle the varying processing loads presented by different research interests. It is designed to handle 256 imput channels at an overall input rate of 256 kHz. The system is designed around a dual bus architecture connected by an interbus window and controlled by a single CPU. All components of the system are commercially available plug in components making replacements simple and system reliability high. This paper describes the system architecture, the system design philosophy and current operating capability.

# INTRODUCTION

The desirability of performing data analysis at sea has been recognized for some time. Until recently, however, the speed and size of array processing equipment has not permitted the high data rates necessary to do spectral analysis and beamforming at sea. Systems were either too bulky to be easily taken aboard ship or too slow to handle the required throughput rates. The Naval Research Laboratory has developed a system

designed around a number of new compact array processors which is easily transported, can withstand the harsh environment at sea, and is fast enough to handle the real time analysis of multichannel systems.

The use of an on-line system such as the one presented here gives the investigator a distinct advantage over the approach of recording a large number of data channels and performing the analysis back in a laboratory facility. One major advantage is that examination of on-line results can verify the quality of the data being taken and changes in the experimental procedure can be implemented if the situation warrants. A second major advantage to on-board analysis is the significant reduction in lag time between data collection and reporting of results. By performing the bulk of the data reduction at sea rather than competing for valuable processing time at the lab system, the investigator can begin the real challenge of interpreting his results as soon as the experiment is complete.

At the time of this writing the system has been used successfully in two major experiments. The first was performed in February and March 1979 off the east coast of New Zealand and involved the angular and frequency distribution of long range reverberation resulting from large broadband explosive sources. The second was performed in June 1979 off the east coast of the United States and involved the angular and frequency distribution of long range propagation from narrowband cw signals. Reports on both of these experiments have been submitted for publication, which attests to the time savings obtained by on-line data reduction. The difference in signal processing requirements for these two experiments demonstrates the flexibility this type of system offers.

This paper discusses the basic system design philosophy and the architecture of the system. The two configurations used for the two sea experiments performed thus far will be discussed to illustrate the flexibility of the design. Finally, an examination of likely directions for system growth will be presented.

# 1. BASIC SYSTEM DESIGN PHILOSOPHY

For a system to be practical as a sea-going real-time research tool it must be compact for easy transportability and easily adapted to a variety of processing needs. In addition, the system must be easily repairable at sea or be designed to allow graceful degradation in the event of partial system failure. The approach taken by the Large Aperture Acoustics Branch at NRL is to, wherever possible, use a number of small array processors which fit directly into the backplane of a DEC PDP 11/34. This creates a very compact system with all the processing elements in standard DEC expansion boxes.

The use of these small array processors offer some real advantages over larger processors. Most processing jobs can generally be split into a number of smaller jobs which can be executed in parallel. By assigning

a different array processor to each phase of the job a high throughput rate can be achieved. Since each job will differ in the amount of processing power needed at a given phase this system permits the movement of power to the points where it is most needed.

By using several processors of the same type a small number of spares can protect against all but the most catastrophic component failure. Should a processor fail when no backup is available it is possible to eliminate some stages of the analysis scheme and continue running in a partial data reduction mode, thus giving graceful system degradation.

# 2. BASIC SYSTEM ARCHITECTURE

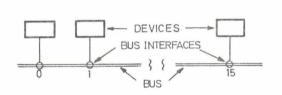

Early in the development of the system the decision was made to design around the DEC UNIBUS. One reason for selecting the DEC mainframe was to provide software compatibility with the large laboratory facility already in use. A second reason for this selection was the widespread industry support of this bus which gives good flexibility in the choice of components.

Since this system is to be used in the potentially harsh environment of a ship a ruggedized version of the PDP 11/34 built by Plessey was selected as the control element for the system. This unit when used with large TOPAZ isolation transformers provides protection from the high vibration environment and somewhat variable supply voltage.

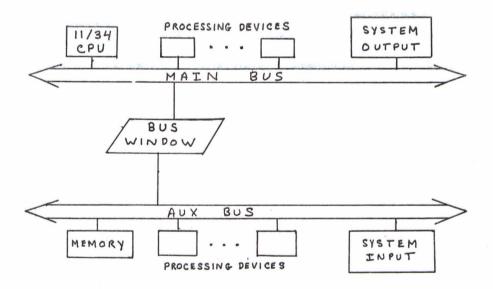

There are two basic constraints which limit any digital signal processing system, namely the amount of memory the system can support and the total data rate the system can maintain. It was apparent in designing toward a system that could handle 256 channels at a throughput rate of 1 KHz per channel that both these constraints would be a problem with the DEC UNIBUS. By using a two bus system, however, it is possible to support nearly twice the memory and to divide the bus traffic so that the data flow does not exceed the bandwidth of either bus. Since most of the processing load is being carried by array processors installed as system devices the load on the CPU is relatively light and a single CPU can control both busses.

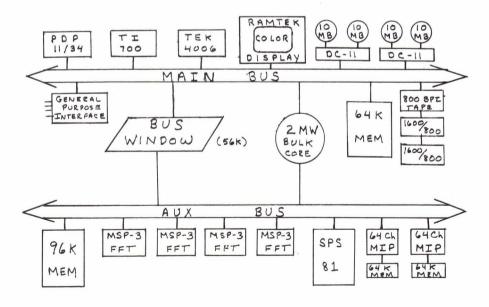

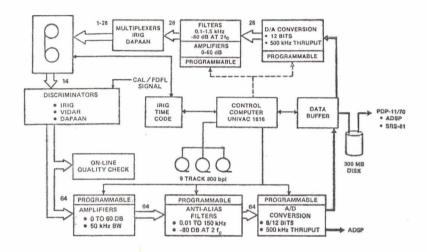

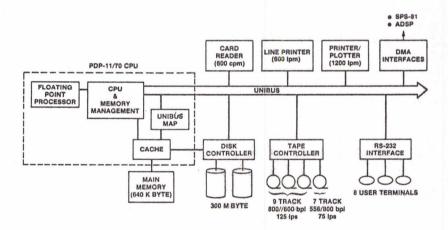

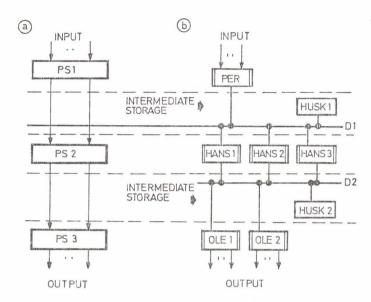

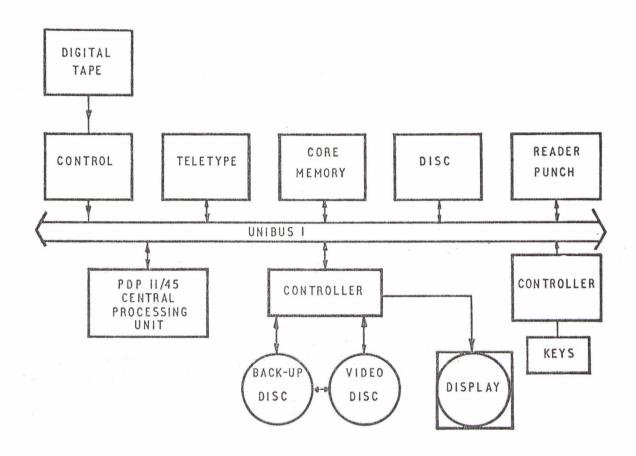

Thus, the basic system architecture (Fig. 1) is designed around a dual bus DEC computer controlled by a single 11/34 CPU. Devices for analog interface, processing, storage, display, and user interface can be moved about as needed for a particular processing job.

# 3. FEBRUARY 1979 CONFIGURATION

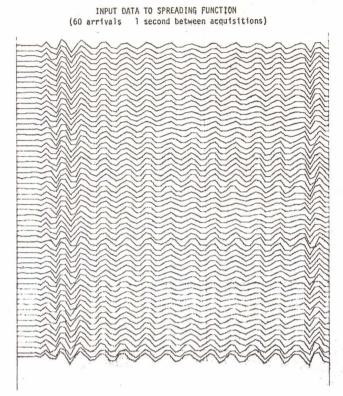

In the February experiment it was necessary to have good spatial resolution, all beam coverage and 100% throughput with broadband sources. The

general analysis scheme was to double buffer the input data, take 1024 point transforms to convert to the frequency domain on each channel, and finally to distribute the energy into the angular domain. The results were then stored on digital tape and displayed for on-line monitoring.

# 3.1 Hardware

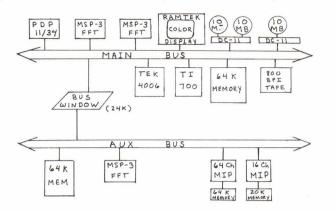

With the basic analysis procedure in mind, it is possible to decide on the specific hardware configuration for this application. The first decision to be made is how to split up the processing between the two data busses. Since the A/D operation can take place without loading a system bus the logical split is to perform the time-to-frequency transform on the aux bus while the space-to-angle transform is handled on the main bus.

To accomplish the A/D and double buffering requirements a pair of Computer Design and Application Micro Input Processors (MIPs) were chosen with enough on board memory to handle 32 channels double buffered on one and 8 channels double buffered on the other. These input processors are smart processors which can be programmed to automatically handle the double buffering needs thus freeing the CPU of this chore.

The main signal processing effort was accomplished using the Micro Signal Processors (MSPs) also by CD&A. Since the time-to-frequency transform can be accomplished with a fast Fourier transform a single MSP card was placed on the aux bus for this purpose. The space-to-angle transform was more complex so a pair of MSP cards were placed on the main bus for this phase of the operation.

This leaves the fairly routine decisions of memory requirements, displays, human interfaces, and storage. The memory requirements are easily handled with 64K memory on each bus. The display is a Ramtek model 9153 color display which offers 256 by 256 spatial resolution with different colors being assigned to each of 256 possible intensity levels. Human interface to the machine was provided by two terminals, one Tektronix 4006 CRT to give plot capability and one Texas Instruments Silent 700 to give hard copy. Two types of storage devices were selected for the system; for permanent retention of data a Kennedy 800 BPI 9-track tape drive was used, while for temporary data storage and off-line analysis three 10 M Byte disk drives were selected. The resulting hardware configuration, shown schematically in Figure 2, fits into a two rack system which is easily transported.

# 3.2 Data Flow

The general flow of data from analog input to digital tape and display is relatively straight forward. The analog input is digitized and auto

double buffered by the two MIPs into their onboard memory. The data is made available on the aux bus through an 8K window which is part of the MIPs. This data is transferred one channel at a time to the aux bus MSP where it is transformed to the frequency domain. The transformed results are placed in the 64K aux memory where they are made available to the main bus through the bus window. The lines of interest are taken by the two main bus MSPs and distributed in angle. The angular distributions for each individual frequency are converted to power and then summed across frequency by the CPU. These average distributions across bands of frequencies are then transferred to digital tape for permanent storage and to the color display for on-line monitoring.

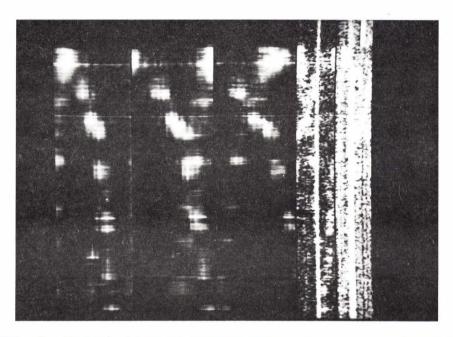

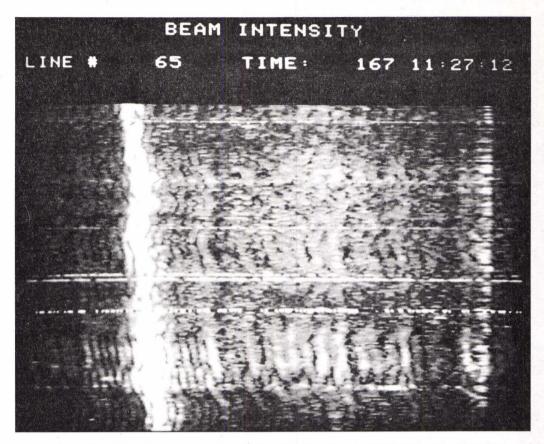

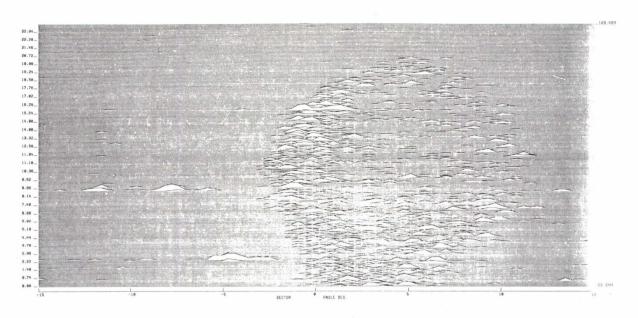

# 3.3 On-Line Results

The results displayed in a real time mode can be a significant advantage in running an experiment. In this case there were three broad bands of acoustic energy being distributed into the time and angle domains plus a pair of cw sources similarly distributed. The on-line display consisted of 64 pixels dedicated to each of the three broadband sources and 32 pixels to each of the narrowband sources, where each pixel corresponds to a given steering direction. This data was sent to the color monitor in a scroll fashion with a new frame being output every second. The result is a display which shows the angular distributions of all bands for the past 256 seconds.

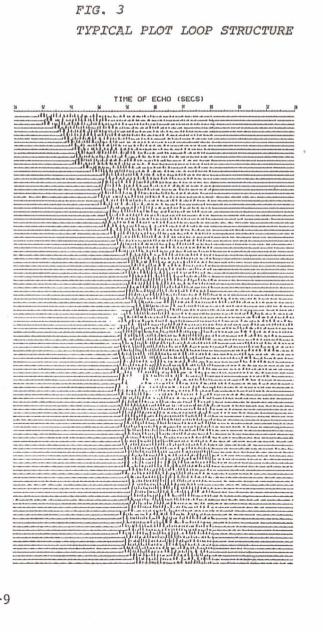

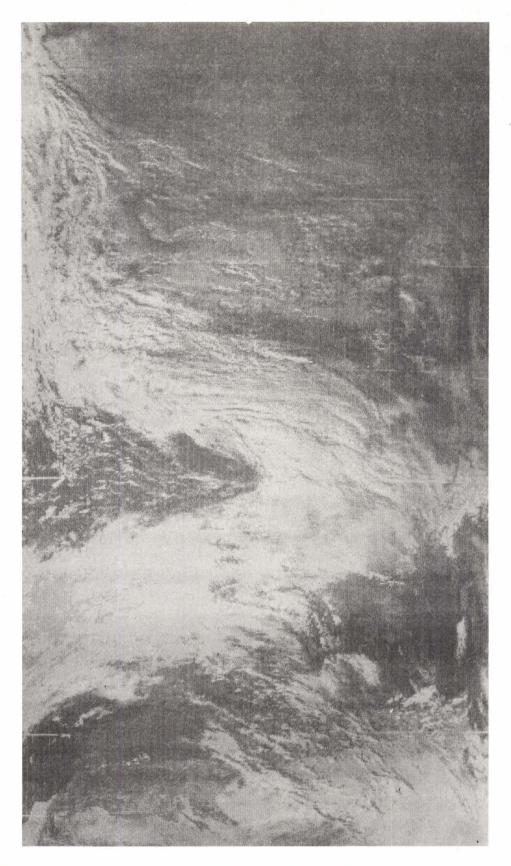

A typical display reproduced in black and white is shown in Figure 3. This shows returns from large topographic features such as seamounts in a time period from about 5 to 9 minutes after the source detonation. As can be seen even in this black and white version, the returns are quite strong and it is clear that data quality is high.

# 4. JUNE 1979 CONFIGURATION

The second use of the system took place in June 1979 off the east coast of the United States. The type of processing required in this second experiment was quite different from the first. In this case, the interest was in a large number of cw sources and good angular and spectral resolution was the goal, while the 100% throughput requirement could be relaxed.

The high spectral resolution, 1/16 Hz, desired implies the need to take long time samples. At the same time the need to obtain a 500 Hz bandpass requires a sampling frequency of 1024 Hz. The resulting sample size required is 16384 for each of 128 input channels.

# 4.1 Hardware

Several hardware changes are imposed by the requirements for this system. The two largest changes are caused by the need to take larger transforms and the need to store 128 channels of 16K words each before transforming can begin.

The large storage requirements were satisfied by placing a bulk memory device capable of holding four megabytes of data. This device, manufactured by Monolithic Systems, appears to the system as an RFll disk system. This device satisfies the storage requirements but does not permit any double buffering of input data. However, since this application does not require a 100% throughput rate this is not a necessary part of the processing.

There are two possible solutions to the requirement of taking 16K transforms. First it is possible to perform the transforms in 4K pieces using the small MSP array processors and then combine the results to acheive the desired 1/16 Hz resolution. Second it is possible to replace the small processor by a large processor which has the capacity to perform the larger transforms. In order to take advantage of previously developed software an SPS-81 normally used in our lab system was selected for use on the sea system.

Two other hardware changes were made for this experiment. The input processors needed to be expanded to handle the required 128 input channels. This consisted of expanding the second MIP to a full 64 channel capability. The final change was dictated by the data output rate. While 100% data throughput was not required it was important not to have large gaps in the data. Hence, no time can be taken for tape changes and additional drives must be added to the system. The final hardware configuration used in this experiment is shown in Figure 4.

# 4.2 Data Flow

The general flow of data in this configuration begins with the digitization and auto double buffering of the 128 input channels by the two MIPs. The data is moved from the MIP memory to the bulk storage device until 16K points have been saved for each channel. At this point the sampling is suspended and the data on the bulk storage is passed one channel at a time to the SPS-81 and transformed to the frequency domain and selected lines are stored in aux bus memory. The data lines are written to tape at this stage so that different shading coefficients can be applied prior to beamforming in the lab facility.

In order to obtain on-line monitoring the data must still be beamformed in real time. Hence, the data is passed on to the MSPs which perform the angular distributions. At this stage, the data is transferred to the main bus to be converted to power and sent to the disks which provide a 2 1/2

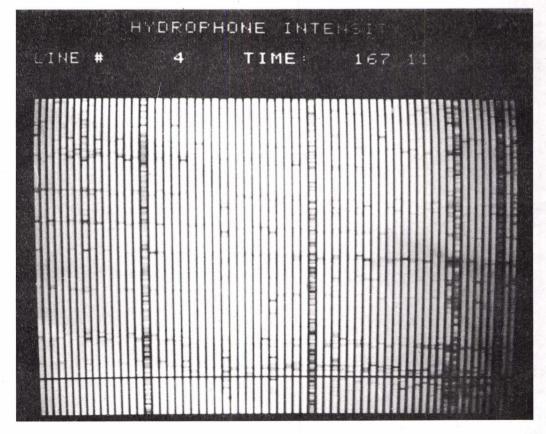

hour display memory. The operator can then select a variety of displays which give a history of either the hydrophone intensities or the angular distribution of energy for any selected frequency bin.

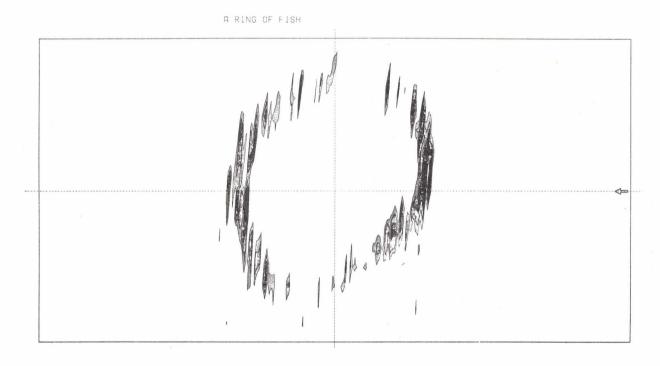

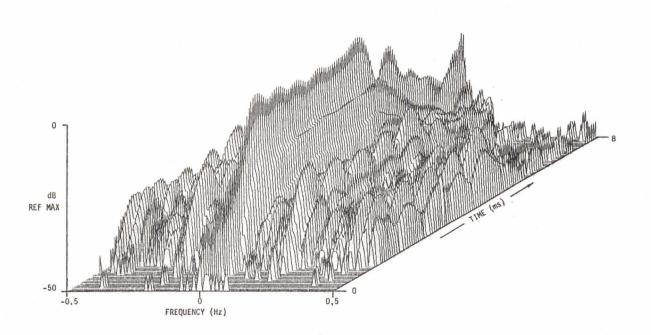

# 4.3 On-Line Results

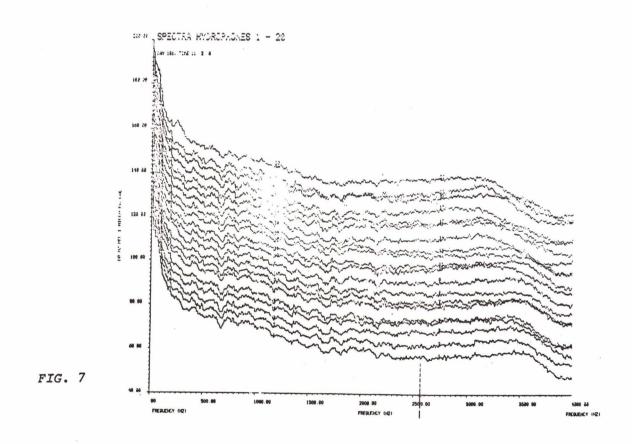

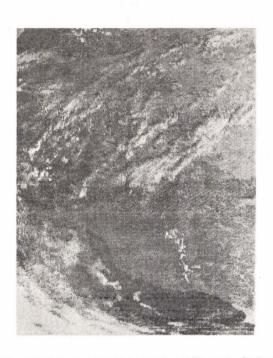

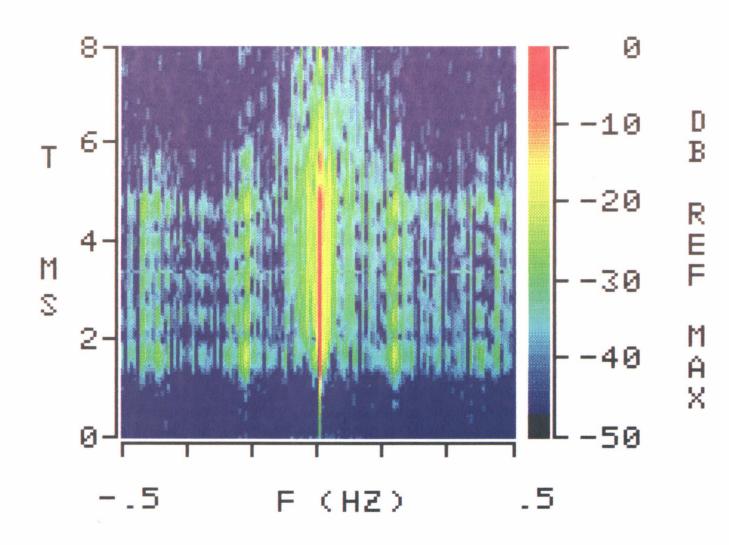

A typical display, again reproduced in black and white, is shown in Figure 5. This displays a 2 1/2 hour history of the angular distribution of one of the possible frequency lines. It is possible to determine from these displays the strength, direction, and Doppler shifting of any of the deployed sources.

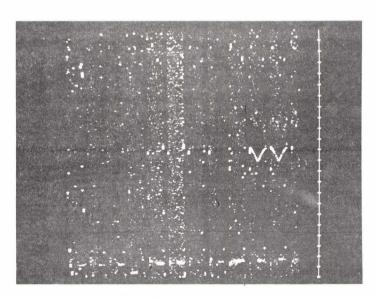

A second type of display is shown in Figure 6 which gives the average hydrophone intensity at a selected frequency as a function of phone number and time. This display can be used to immediately identify dead or weak channels and permits early correction of such problems.

# 5. DIRECTIONS OF SYSTEM GROWTH

While the basic system design has worked quite well in two quite different experimental applications some system improvements are called for. The three general areas of system growth are; increased channel capability, increased CPU speed, and greater array processing capability.

The channel capability will soon be expanded to the original design goal of 256 channels with the addition of two fully expanded MIPs. It has become apparent in the last two experiments that software development will be greatly simplified on the expanded system with the addition of a faster CPU. For this purpose a PDP 11/55 will replace the slower 11/34 as the main system CPU.

The final system change will be in the choice of an array processor capable of handling the large transform sizes needed in future experiments. While the SPS-81 is capable of the speed and size requirements it has two disadvantages. First, it is considerably larger than the card size MSPs which presents some transportation problems. Second, by using a single large processor, such as this, it becomes a critical link in the system and the system cannot be gracefully degraded if it should fail. One solution being considered is to use a number of the small MSP processors along with a second CPU as a custom made array processor. By using components identical to the ones already on the system spares are easily available and graceful degradation is possible.

#### CONCLUSIONS

The system developed by the Large Aperture Acoustics Branch at NRL was designed to be versatile, compact, and reliable. The early implementations of this system, which have been presented here, have been quite successful and have confirmed the validity of the basic design. Future system improvements will make the system capable of performing both frequency and angular distributions at an input rate of 256 KHz.

#### DISCUSSION

- J.S. Pyett With 256 channels at 1 kHz, what is the word-size and the percentage loading on the auxiliary bus?

- $\underline{J.M.}$  Griffin The wordsize referred to is 12 bits from the A/D converter. Once on the bus, however, we are actually transferring 16-bit words since no packing is done. I would estimate the total bus load for all DMA's on the auxiliary bus at near 50%.

- <u>D. Steiger</u> Is any processing done other than in the array processor?

- J.M. Griffin The only processing done by the CPU are the simple tasks such as block floating to true floating conversion and averaging of data after it has been reduced.

- D. Steiger What data is recorded?

- J.M. Griffin The data recorded varies with the experiment. In the January configuration we were writing beam power in three frequency bands as a function of time. In June the output was a set of frequency estimates for each hydrophone. Although the beam power was computed and displayed, this does not represent a data reduction so no tape is saved. In addition writing the frequency estimates permits application of a variety of weighting coefficients or phase corrections after the fact since phase information is not lost.

- D.V. Crowe What operating system do you use?

- J.M. Griffin Software development is done under RSX 11M. Once complete the program is booted from disc and runs in a stand-alone mode.

- $\underline{\text{R. Seynaeve}}$  How much effort was involved in say the preparation of the June experiment?

- J.M. Griffin From a software standpoint, after the development of a general approach, approximately three man-months were used. It should be pointed out, however, that some of the routines, such as those to drive the SPS, had been previously developed.

R. Seynaeve How do you synchronize data?

26

J.M. Griffin Each device has interrupt capability. Typically the interrupt routine consists of setting a flag. A master scan loop is written to start the devices in proper synchronization.

R. Seynaeve Is data transfer by DMA's?

J.M. Griffin Yes, all the major devices have DMA capability.

$\frac{R.\ Seynaeve}{find\ colour}$  Do you experiment with pseudocolour and do you

J.M. Griffin We have not made a scientific study of pseudo-colour. This particular table was developed by trial and error to be intuitive, not to display maximum information. I believe colour can be of significant advantage in distinguishing intensity levels, although a different colour table would certainly be chosen for this.

FIG. 1 BASIC SYSTEM ARCHITECTURE

FIG. 2 SYSTEM CONFIGURATION FOR FEBRUARY 1979

FIG. 3 ON-LINE ANGULAR DISTRIBUTION OF BROADBAND RETURNS FEBRUARY 1979

FIG. 4 SYSTEM CONFIGURATION FOR JUNE 1979

FIG. 5 ON-LINE ANGULAR DISTRIBUTION OF NARROWBAND SOURCE

JUNE 1979

FIG. 6 ON-LINE HYDROPHONE INTENSITY DISPLAY

JUNE 1979

SEYNAEVE et al: SACLANTCEN system

SACLANTCEN REAL-TIME SIGNAL PROCESSING SYSTEM

by

R. Seynaeve and P.A. Boni, V. Duarte, M. McCann, P. Nesfield SACLANT ASW Research Centre La Spezia, Italy

To meet its increasing requirements in real-time signal processing, SACLANTCEN has developed a general purpose signal processing system called WARP to be used with a fairly wide range of underwater acoustic research projects. achieve a high throughput and an easy programming, WARP is organized in several subsystems corresponding to the successive signal processing tasks to be performed, each subsystem being relatively independent from the others. Great emphasis has been given to the software and the system interfaces with the user and to the on-line testing and debugging facilities. One of the aims is in fact to make the control and programming as easy as possible, through the use of special purpose languages and interactive methods, thus providing the flexibility and reliability required by the research projects. Because of the wide range of requirements WARP is configurable into larger and smaller systems, all using the same hardware elements, operating system and high-level language.

### INTRODUCTION

In the early 1970's the Centre's needs in real-time signal processing were generally met by using mini-computer systems with hardware Fourier processors, together with specialized software for acquistion and signal processing, such as ITSA and SPADA [1,2]. Over the last few years the requirements have increased considerably, and a new family of systems called WARP I has been designed to meet the current and future needs of a fairly wide range of underwater research projects.

# DESIGN CONSIDERATIONS

Among the most important design goals were the following:

- (a) <u>High Throughput</u>: The system was to be used in experiments with multi-sensor arrays and large band-widths.

- (b) <u>Variable Configuration</u>: To cover a fairly wide range of requirements, WARP was to be configurable from a basic set of elements, into specific array processor based systems, all with the same macro languages and operating systems.

- (c) <u>Fast Response to User Requirement</u>: The system hardware architecture and software design was to allow easy and reliable programming even for complex tasks.

- (d) <u>Directly Programmable by Users without extensive</u> <u>computer experience</u> and, therefore, general use of interactive methods and macro languages.

- (e) Special attention to display/graphic end.

- (f) <u>Hardware reliability</u> and therefore possibly graceful degradation for the larger systems, and self-tests of subsystems during run time.

### SYSTEM DESCRIPTION

### 2.1 System Overview

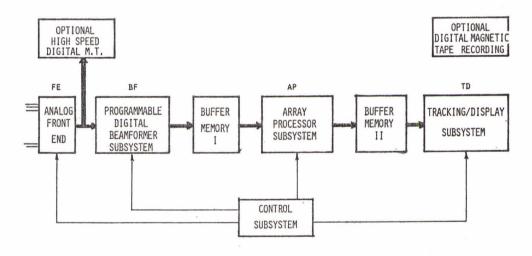

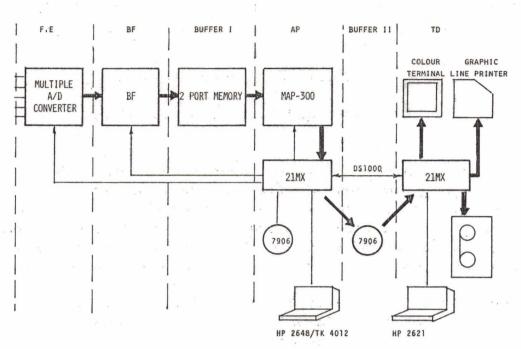

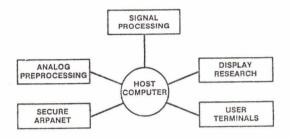

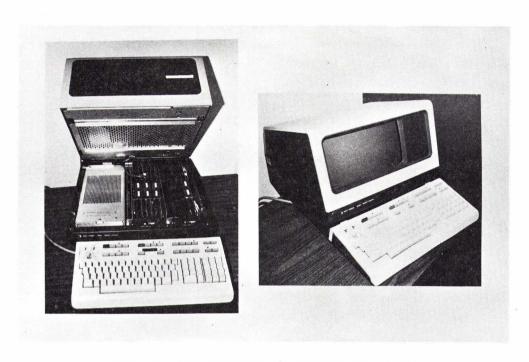

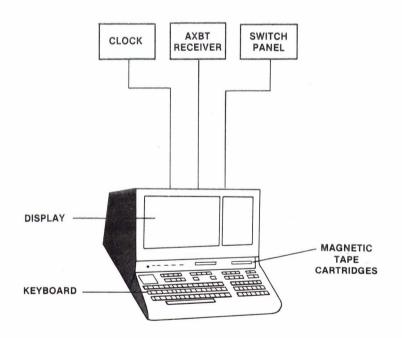

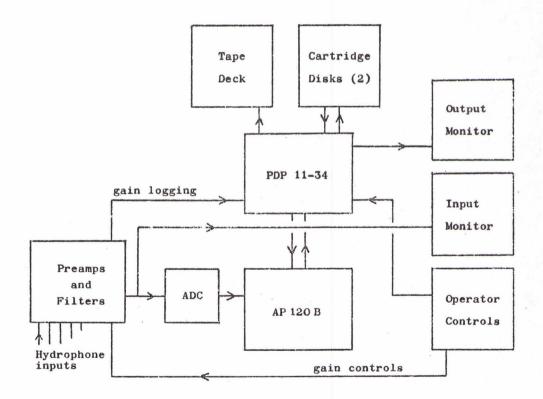

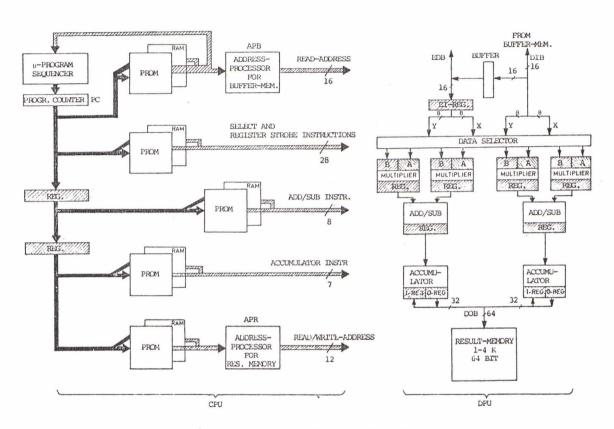

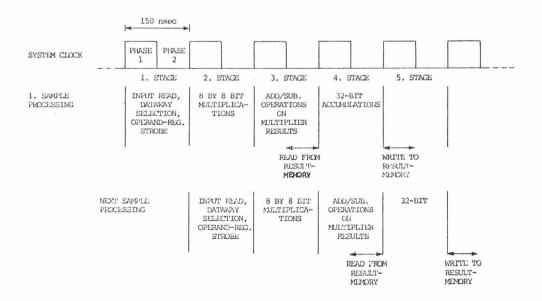

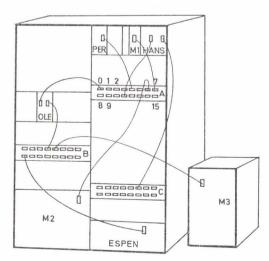

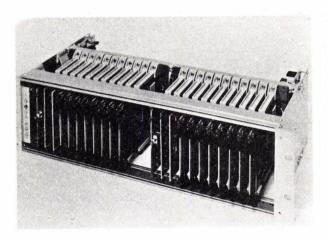

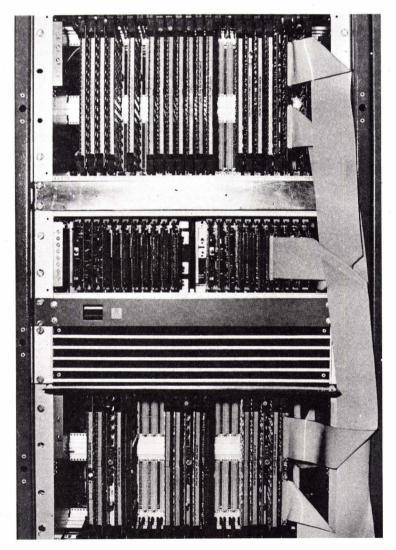

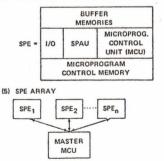

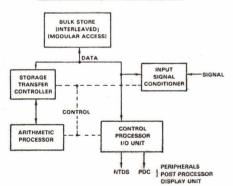

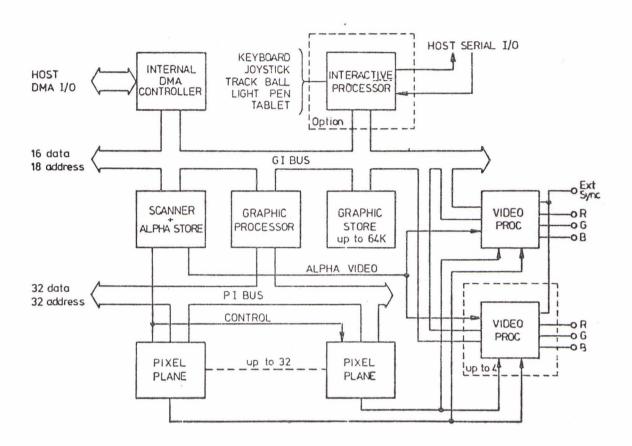

Figure 1 shows the functional block diagram of an average WARP configuration, such as used in some towed-array sonar experiments. Figure 2 shows its actual implementation.

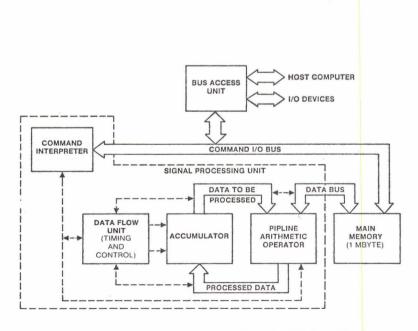

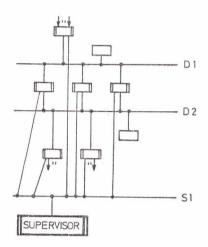

(a) The various functions are performed in well defined subsystems: spatial processing in the beamforming subsystem (BF), frequency and other processings in the array processor subsystem (AP), tracking/display/graphics (TD) and control (CO) in the corresponding subsystems. The data synchronization problems between subsystems are eased through the use of the buffer memories I and II.

Buffer II is especially large, therefore, uncoupling the tracking/display end from the on-line processing. As the three subsystems are well decoupled, the programming is easier and more modular, it can more easily be done by separate programmers and the final integration is quick. These factors are of major importance in a multi-project research environment where a quick reaction time to new or changing requirements is a very important point.

- (b) The arithmetic can accommodate a large dynamic range: 24-bit arithmetic in the BF with 16-bit block floating output, 32-bit floating point (sometimes 16-bit floating point) in the AP, and 32-bit floating point in TD.

- (c) The software reflects the decoupling of the hardware implementation: upon the selection of an operational mode, the control subsystem despatches the appropriate programs and parameter files from the subsystem's libraries to each of the subsystems and starts the processing sequence; many such modes can be prepared individually and stored for an experiment or, alternatively, assembled at sea as the need arises. The subsystem's programming is largely based on the use of interactive methods and special macro languages.

- (d) The storage of input and/or output of the data depends on the application and uses peripherals ranging from a 42 Megabit/s very high speed tape recorder or a large disc at the input to a 1600 bpi/75 ips computer tape recorder at the output.

- (e) The configuration of Figure 2 can be reduced to smaller ones supported by the same software but where, for example, there is no time domain beamformer, and where the output computations are made in the control processor; alternatively, in some situations, another control processor driving continuously the BF [see para 2.2] and performing other external measurements can be necessary. Such modifications to the system are easily implemented because of the flexibility provided by a modern multiprogramming operating system (RTIV) which includes a good distributed computing software (DS 1000).

The following sections will further describe the various parts and subsystems.

# 2.2 The Host Computers and Discs

Each of the BF, AP and TD subsystems require support from a host CPU (the FE needs very little). In many applications the BF needs little more than the loading of microcode at the time of setting up a mode of operation and the monitoring of the scaling of the output data. In other applications, where the beamforming is time varying, or recording on disc is required at the level of the beamformer, a CPU dedicated to the BF subsystem can be necessary. The AP and TD require a continuous service, but in the applications where fairly straight forward graphics are required with little operator interaction, one CPU with enough memory can often suffice for both.

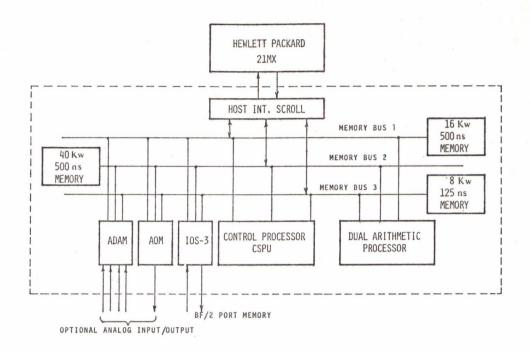

In other words, a system can include from one to three host CPU's. The model used is the Hewlett Packard 21MX E and F versions with 7906 20 Megabyte moving head discs. The F version which has a floating point processor is somewhat faster. It is basically a 16-bit mini with a 350 ns extended memory (up to 1 Megaword) accessable through a dynamic mapping system. It can be microprogrammed (arithmetic and I/O) by the user. Typical times for the 21 MX-F are:

|                         | Single<br>Precision | Double<br>Precision |

|-------------------------|---------------------|---------------------|

| Floating Point Add      | .63 µs              | .68 µs              |

| Floating Point Multiply | 1.78 µs             | 2.75 µs             |

| Sin                     | 47 ms               |                     |

| Sqrt                    | 30 µs               |                     |

| <sup>log</sup> 10       | 50 µs               |                     |

The 21MX's Real-Time IV multiprogramming operating system includes many interesting features among which a file manager, a distributed system software (DS 1000) and the handling of large arrays. The 7906 disc has a 10 Megabyte removable cartridge and its controller can handle several CPU's and several discs, allowing to implement some very interesting configurations.

It is important to note that in a WARP multi CPU configuration, it is usually possible to reconfigure the system with one CPU only, if the need occurs, however, at the cost of an overall slowing down.

# 2.3 The Analogue Front End

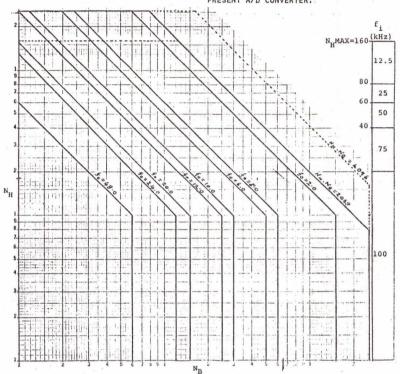

As will be seen in the next paragraph, the type of beamformer used requires that the data be sampled well above the Nyquist rate for accurate beamforming. The remote controlled front end, which was designed by the Centre's Electronic Department, allows for the simultaneous sampling of up to 80 inputs (expendable to 160) at the following rates

| Number of Inputs | Max A/D Conversion Rate/Input |

|------------------|-------------------------------|

| 1 to 20          | 100 kHz                       |

| 21 to 40         | 75 kHz                        |

| 41 to 60         | 50 kHz                        |

| 61 to 80         | 25 kHz                        |

| 81 to 160        | 12.5 kHz                      |

It should be noted that the simultaneous sampling of the inputs is not necessary for beamforming as the delays between sampling times could be compensated in the beamforming microcode. However, as in several applications the beamformer is bypassed, simultaneous sampling provides often more simplicity in the successive signal processing.

# 2.4 The Programmable Digital Beamforming System

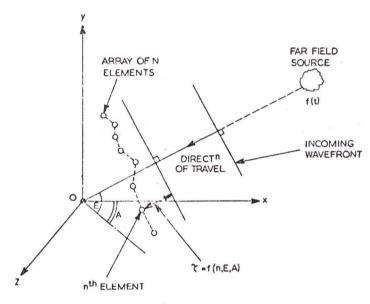

### 2.4.1 The Beamformer

In mid 1977 the Centre issued the specifications for a programmable beamformer, the development of which was awarded to PLESSEY, U.K. The equipment was delivered at the end of 1978 and has been in operation since.

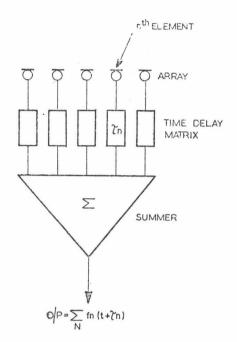

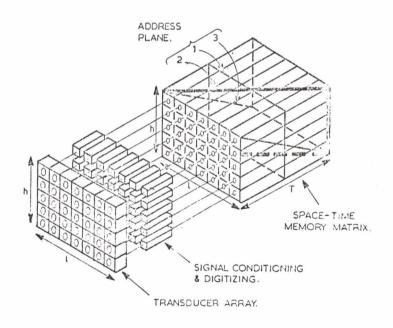

This beamformer is of the partial sum type, i.e., as the wavefront travels along the array, the contributions of each hydrophone to each of the output beams are accummulated in ad hoc memory locations ("partial sum memory"), which correspond to the output beam samples. A value in such a location is outputted as a beam sample when all the contributions for that beam sample has been received. No memory is required at the input and thus a high input sampling rate, giving a high accuracy in the beamforming, is easily achievable. This beamformer implementation is specially interesting when a high input time resolution, a large number of hydrophones and a relatively low number of beams are desired.

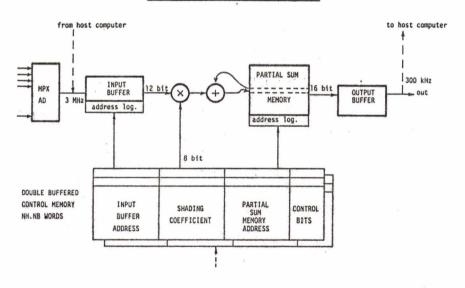

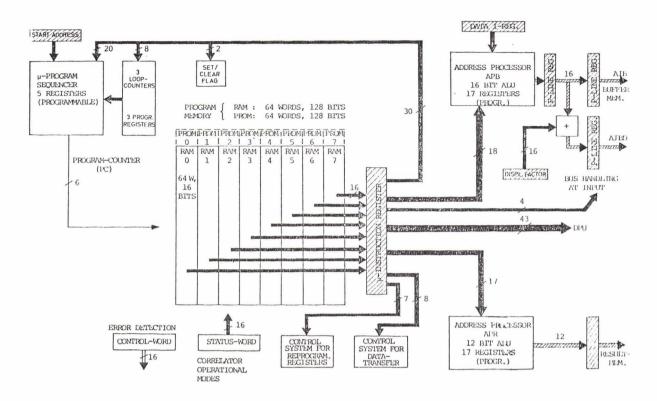

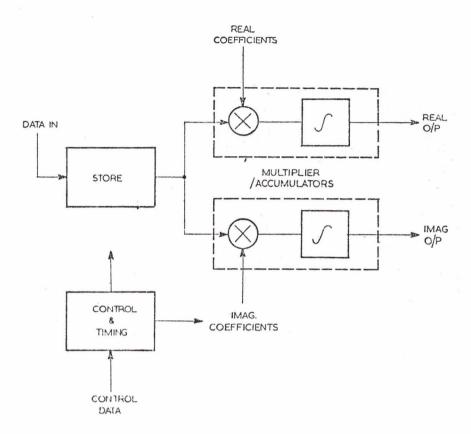

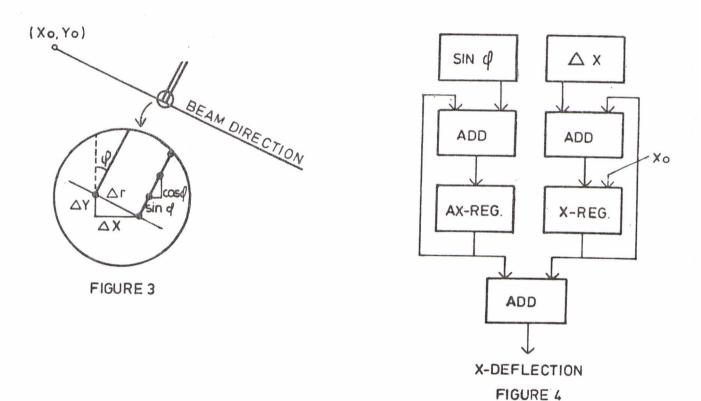

The implementation is made as a microprogrammable pipeline processor as shown in Fig. 3. The input data is sampled at high rate (typically 16 times Nyquist frequency) and is temporarily stored in the small input buffer. The long words of the control memory each contain the address of an input sample, its shading coefficient, the address of the partial sum location where it must be added, and several control bits, including one which is set when all contributions have been received and the sample can now be output. There is one such control word per hydrophone and per beam. The beamforming performed is thus entirely defined by the control memory content, and therefore beamforming can be done in 1, 2 and 3 dimensions, with any shading and any beam direction, this provided a set of limiting relations is respected [Fig. 4]. There are two separate program memories and the control can be moved from one to the other in only one memory cycle; feature allows to implement various types of time varying beamforming. The main specifications of this beamformer are as follows:

Maximum number of sensors : NH = 255

Maximum number of beams : NB = 255

Control store :  $NH \cdot NB = 2048 \times 48 \text{ bits}$

(expandable to 4096)

Partial sum store: 4096 x 24 bits

(expandable to 16384)

Input buffer: 8192 x 12 bits

Output buffer: 4096 x 16 bits (expandable to 8192)

Multiply/add rate: NH · NB · fo ∠3 MHz

Maximum input data rate: NH·fi 43 MHz

Maximum fi/fo: 255

Input word: 12 bits

Shading word: 8 bits or 7 bits + sign

Arithmetic/partial sum word: 24 bits

Output word: 16 bits selectable out of the 24 bits

of the partial sum memory.

DWING THE

# 2.4.2 Software and Development Aids

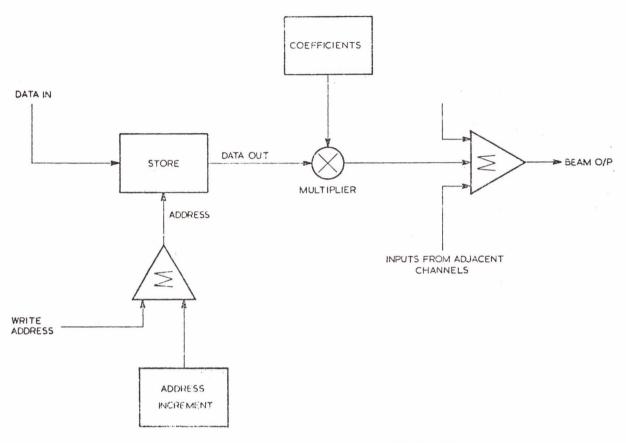

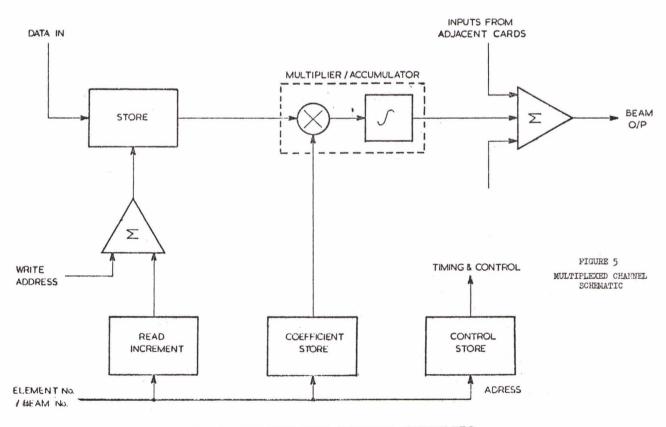

The beamformer subsystem is supported by BF-M, an interactive program for beamforming microcode generation. The user specifies the geometry of the array, the direction of the beams, the shading coefficients of each sensor for every beam. This results in a table of parameters which is used by the microcode generator; both the microcode generated and the parameter table can be filed away. Means are available to readily edit ASCII parameter tables or microcode.

Program BF-SIM allows to synthesize and send families of wavefronts to the BF and to display the measured beamforming patterns to check the beamformer design and monitor quantizing effects.

# 2.5 The Array Processor Subsystem

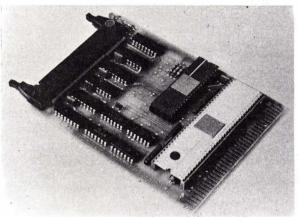

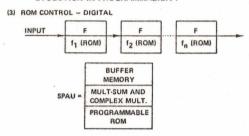

#### 2.5.1 The MAP 300

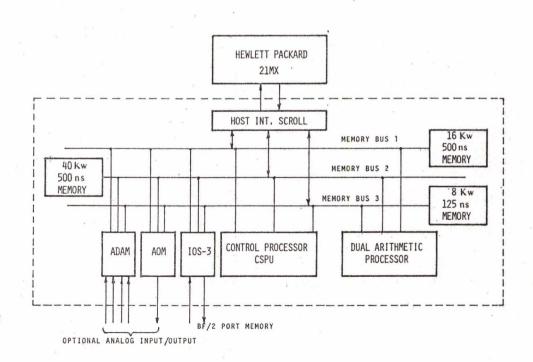

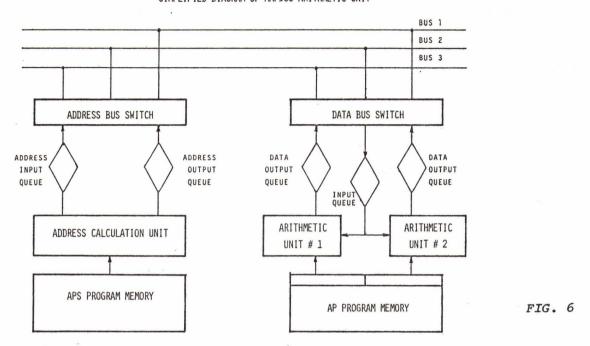

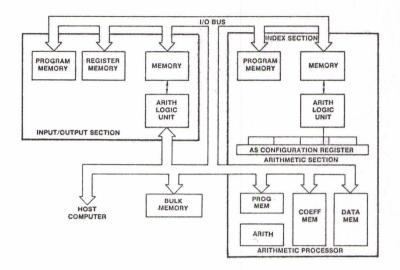

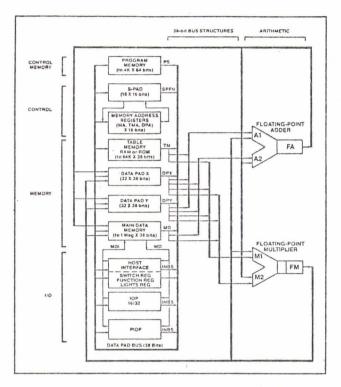

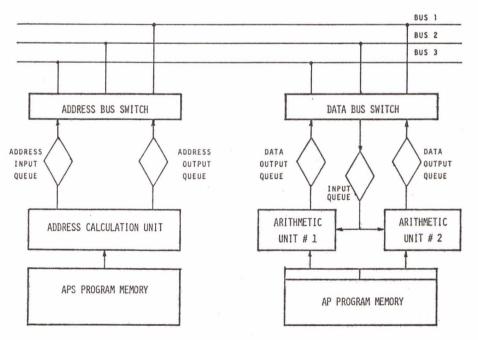

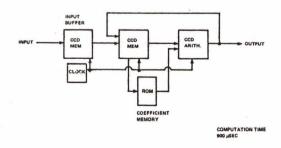

The array processor is the central element of the WARP system. The model selected is the CSPI MAP 300, a block diagram of which is shown in Fig. 5. Its principal components are:

- (a) A dual pipelined arithmetic unit with inputand output queues and separate address computation unit[Fig. 6], capable of about 5 million multiply-add per second.

- (b) Three memories; one high speed (160 ns) of 8192 words of 32 bits (bus 3), and two medium speed (500 ns) of 40960 words (bus 2) and of 16384 words (bus 1) both of 32 bits.

- (c) A control processor (CSPU)

- (d) A host interface processor (HIM)

- (e) One or more input/output processors (IOS, ADAM, AOM).

The three memories are connected to all the other elements through their multi-port buses; however, the executive and programs run usually on bus 1 memory, while the data are stored on bus 2 and bus 3 memories.

Some of the most interesting features of this processor are its speed, its modularity, its flexibility in input/output, and the real-time features of its operating system.

Most of the AP programming is normally written in SNAP (CSPI's macro-language for signal processing) which is very comprehensive and allows for very good communication with the external world. Some excellent features are:

Logical rather than absolute buffers.

Several data formats (32 bits, 16 bits and 8 bits, fixed and floating).

Ability to handle several I/O processors concurrently. Its buffer protection in arithmetic and I/O processing.

A more detailed presentation of these features, with their meaning to the programmer, are given in a separate paper [3].

# 2.5.2 Speed Considerations with SNAP

As SNAP uses an interpreter, the time taken by the MAP to perform an operation consists of the execution time itself and the executive's overhead required to load and start the various MAP modules. The execution time is usually proportional to the block length, while the overhead time is fixed but can be more or less overlapped with the execution time of the previous operation.

With the current software, on the average, at a block size of about 256, the overhead time becomes about equal to the executing time. Using a technique called "binding", where sets of consecutive operations are linked together and stored under a new function name, the overhead time can be reduced to about 250  $\mu$ s at the expense of more program memory. A further improvement called "stacking" should be available shortly from CSPI. To summarize, the relative speed of the MAP will increase if the data are processed in large blocks (typically 1024 words and above).

# 2.5.3 Software and Development Aids

At SACLANTCEN over the last nine years, interactive techniques have proven very effective for the design and trouble-shooting of signal processing systems in a quickly changing research environment [1]. Our first experience with the MAP confirmed quickly that here too such techniques would be of great use:

- (a) We extended SNAP with AP-M, an interactive monitor which allows to create a signal processing program, step through it visualizing buffers on CRT's, variables, and tables on a terminal, with the possibility of quickly modifying it and observing immediately the effect of the change without recompilation.

- (b) We developed a facility called AP-STROBE which allows to observe through a separate I/O processor any buffer, table, variable etc., of the MAP operating at full speed in real-life conditions and at a point in its program externally selectable by the operator. The same can be done repeatedly, storing the "film" of the observations in a file to examine them at a lower rate.

- (c) As delivered by CSPI, SNAP appears as a good macro language for signal processing. The I/O is powerful but still requires that the user handles the data traffic and peripheral control in the host if the MAP needs to access them. We are currently preparing a new software that will allow the buffered access to all the host peripherals using very simple calls in SNAP. In this way the user will be able to program almost exclusively in an extended SNAP, the host becoming from the user's point of view essentially a transparent peripheral controller.

# 2.6 The Tracking/Display Subsystem

In a number of applications further processing between the AP and the display is required: tracking, plotting programs, sorting of data. For this processing the TD subsystem may, according to the application, run in a memory partition of the control CPU or have its independent small computer. The data are passed from the AP to the TD through a 20 Megabyte disc. In this way the output processing is well decoupled and this is specially useful when the experiment monitoring requires operator's interaction at the display level.

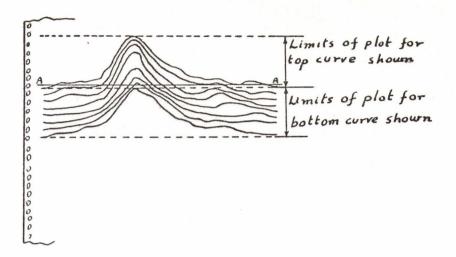

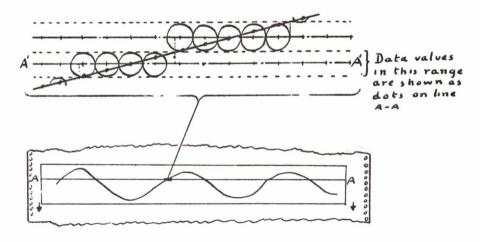

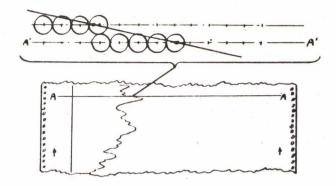

WARP's visual output subsystem is presently oriented towards two rather different peripherals: a high resolution video colour console, and a dot-matrix graphic lineprinter. The colour system is aimed at pseudocolour displays of physical data and at sonar console applications, whereas the graphic dot printer is especially useful for multi-curve displays and pseudo grey-tone representations; it is also quite cheap to operate for large productions and allows for one inexpensive device for both graphis and lineprinting.

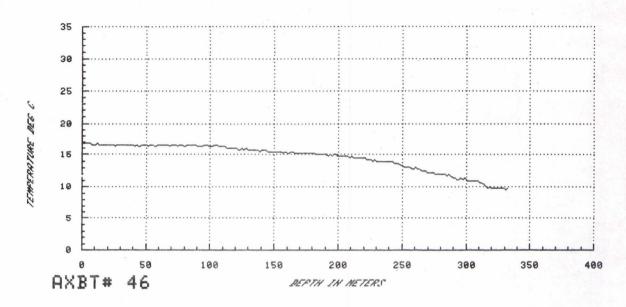

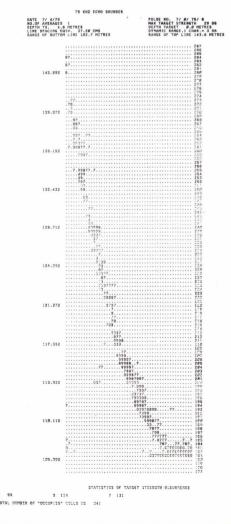

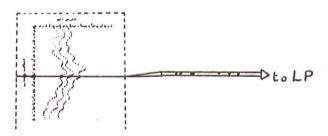

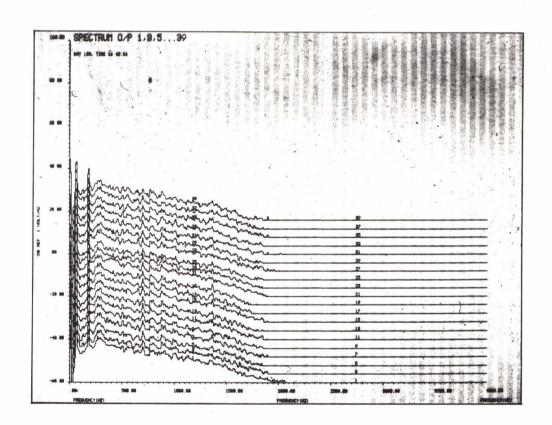

# 2.6.1 The Graphic Printer

It presently uses a Printronix 300 line/minute dot matrix lineprinter in the graphic mode, a device somewhat comparable to a Versatec printer/plotter. It has, however, less resolution but is cheaper and uses normal paper instead of the special paper required by the Versatec. The software developed at SACLANTCEN is oriented towards the problem of plotting many curves simultaneously in several different ways for sonar, propagation and sea-floor studies; also the control of the subsystem has been made quite easy to reduce development time and increase flexibility during experiments. As this subsystem is described in detail in another paper [4], no more will be said here about it. An example of a typical output is shown in Fig. 7.

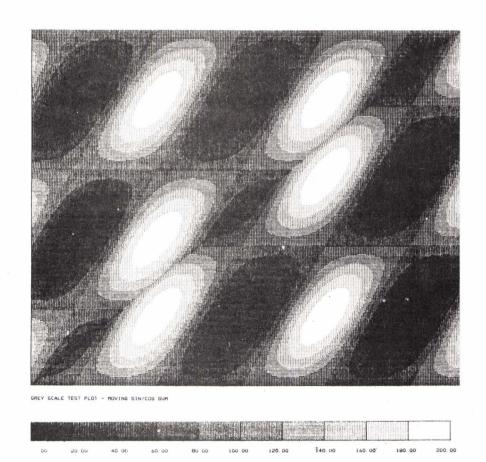

#### 2.6.2 The Colour Station

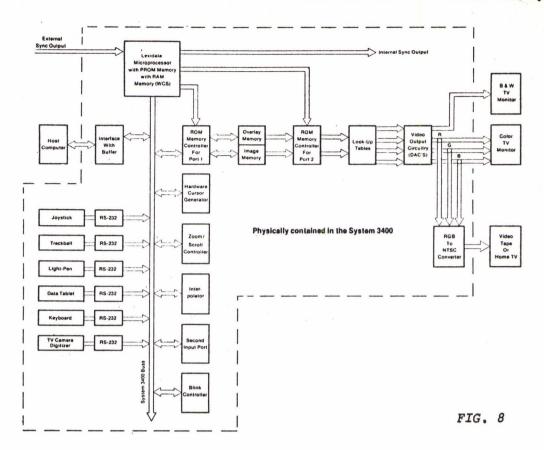

Colour can be most useful to represent data which are functions of two or more variables. Black and white representation using contour lines with figures are accurate, but can be lengthy to examine, and it is often difficult to associate mentally different areas of equal level, which is easier with colour. Grey tones can be used too, but we usually found it unsatisfactory with representations of scientific data, like spreading functions or propagation loss versus range and frequency, one possible exception being remote sensing images. We had good results with colour in a number of cases, including running spectra, spreading functions and remote sensing.

Initially, WARP used a simple system with three planes of  $256 \times 256$  pixels but has just now received a LEXIDATA 3400 with 10 planes of  $640 \times 512$  pixels and two overlay planes [Fig. 8]. It includes black and white, and colour look-up tables, blinking, hardware zoom and track ball. The 10-bit resolution is required mainly for remote sensing applications. The display is driven from a separate terminal on a slave 21MX CPU or on the 21MX of the control subsystem according to the configuration.

A major problem with colour is how to obtain hard copies. We are presently using small and large (8" x 10") polaroids but we are completing a software to store images on magnetic tape for playback on the APPLICON colour jet-plotter system, on the Centre's UNIVAC 1106. We expect to see by next year a new cheaper model designed to operate directly from a colour raster scan display like the LEXIDATA 3400, and which could be taken on board during sea trials.

#### 2.6.3 Software

Both display subsystems are supported by software (currently still partially under development) which includes:

- (a) The retrieval of the data from the buffer disc following defined procedures, or under the operator's control.

- (b) Facilities for easier preparation of the plot or image.

# 2.7 The Control Subsystem

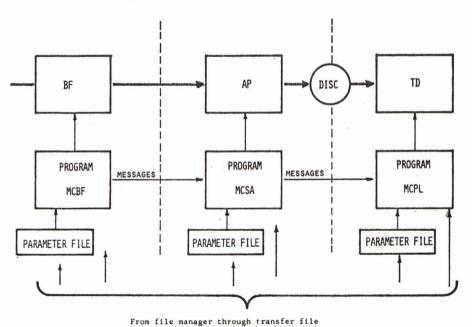

The control subsystem is not a physical entity but corresponds to various program loading, data communication and program control procedures in the overall system. It encompasses:

# (a) System Loading and Start-up

Each mode of operation in WARP is defined by a set of programs and parameter files operating in the subsystems. The loading is done using a "transfer file" i.e., a file that contains commands to be executed by the file manager [Fig. 9]. The transfer file is usually given a name related to the mode of operation.

# (b) Parameter Files and Program Control

All programs in the AP, BF and TD subsystems run from well defined ASCII parameter files. Figure 10 shows such a file for the MCPL (Multi-Channel Plotting Program). A key feature is that each line starts with a two-letter code identifying the program parameter(s) concerned by the numerical value(s) on the line. Two asteriks indicate a "comment" line. As the programs use default values, only these parameters that need modifications must be present in

the file. The parameter files can be edited using a standard editor, or a special one to handle tables more conveniently. This type of parameter file has proven very useful and is now completely adopted in all our systems.

# (c) Program-to-Program Communication

The BF, AP and TD subsystems operate with independent programs. Information on the data such as sampling frequency, number of channels, scale factor, etc., is passed between these programs through a "mail-box" system; a program can send a message to "system available memory", where another program can check for its presence and get it. The implementation is conveniently done using RT IV's class I/O. If the programs run on different CPU's the message are sent through the DS1000 links.

# (d) Operator Control

On a small system where one CPU only can support the BF, AP and display, one terminal can often support the RT IV system control and the operator's dialogue with specific programs. In certain cases it is more convenient to separate the two functions using two terminals. This is usually so when the TD subsystem requires much operator interaction and includes its own CPU.

# LOGISTICS AND RELIABILITY OF OPERATION

During the more important sea trials, a full set of spares is available on board, which includes:

One 21MX CPU (minimal memory)

One 7906 disc

One MAP 300 (minimum configuration)

One full set of BF boards (except back plane)

In addition to this, the system has a great capacity for reconfiguration to face the breakdown of a CPU, disc and of minor peripherals.

Back in the laboratory, and often at sea, the spare equipment is usually operated as hot spares in smaller systems. Except for the BF, another complete system can be operated on shore while the first system is at sea. Spares on shore are not available for the AP as there is more time available for repair and as the jobs are usually less critical.

The BF has proven entirely reliable over almost one year. The MAP has had few breakdowns: two power supplies and one ROM chip. The various HP 21MX and 7906 discs gave some problems in the early part of their lives.

### CONCLUSIONS

We have described a system designed for high-speed signal processing where the objective has been to simplify drastically the programming without any loss of throughput and of generality within the application field concerned. Experience with the system over several applications has proved the validity of the concepts proposed.

Work is continuing to bring the system to the level where it can be put in less experienced hands, and to complement its basic set of signal processing and display/tracking modules.

# REFERENCES

- 1(a) SEYNAEVE, R. and HOPFORD, P. Interactive signal processing with a mini-computer system, presented at DATAFAIR, U.K., 1973.

- 1(b) ITSA Manual, Real-Time Systems Department, SACLANTCEN La Spezia, Italy, 1977.

- 2(a) BARBAGELATA, A., BONI, P., DIESS, B. Operation Manual for SPADA, SACLANTCEN SM-80, La Spezia, Italy, SACLANT ASW Research Centre, 1972.

- 2(b) SPADA Operator's Manual, Real-Time Systems Department, SACLANTCEN, La Spezia, Italy, 1977.

- 3. NESFIELD, P., Experience with a MAP 300 array processor, In: "Working Level Conference on Real-Time, General-Purpose, High-Speed Signal Processing Systems for Underwater Research", SACLANTCEN CP-25, La Spezia, Italy, SACLANT ASW Research Centre, 1979.

- 4. McCANN, M.J., Graphics for real-time signal processing systems, In: "Working Level Conference on Real-Time General-Purpose, High Speed Signal Processing Systems for Underwater Research", SACLANTCEN CP-25, La Spezia, Italy, SACLANT ASW Research Centre, 1979.

#### DISCUSSION

- H. Urban Is the MAP system now working properly, or are there still software and hardware errors in the system?

- R. Seynaeve We know in great detail of the problems encountered by CSPI with their first MAPS. Our first unit was delivered in December 1977 after CSPI had moved to the multiwire technology, which seems to have cured all their interference problems. Our first unit has performed very reliably over  $1\frac{1}{2}$  years. Due to combined hardware/software reasons the MAP did not run at full speed when delivered and we accepted it with reservations, but CSPI has since corrected this with appropriate upgradings. The software is excellent and has very few errors. More details are given in another paper by P. Nesfield.

- D. Nairn What language is the system basically written in?

- R. Seynaeve The system is written in HP assembler and Fortran.

- $\underline{\text{D. Nairn}}$  Do buffers between the subsystems cause a speed penalty?

- R. Seynaeve The buffers between the subsystems do not introduce any speed penalty, but only a slight delay as the system is basically a pipeline.

- <u>H.J. Alker</u> Was it necessary to modify the RTE-IV operative system for including the multi-processor concept?

- R. Seynaeve No, the system uses a standard RTE-IV with DS100 (the HP distributed system software). We have developed some extra system software: for example, drivers and EMA support routines.

- <u>H.J. Alker</u> What has been done for monitoring in real-time hardware and software errors? And, was the system described limited by not having such a monitor system available?

- R. Seynaeve We feel we should include run-time automatic tests of the whole system, but this requires time to develop. The hardware, especially the beamformer and the MAP 300 have been very reliable. Also, at this stage, when in operation the systems are usually attended and therefore this problem has not yet been important.

- <u>W.G. Wagner</u> Can the array processor be shared by several users concurrently?

- R. Seynaeve For normal processing, we do not consider sharing the array processor between several users. Most of the applications where we use array processors are computation intensive and, if anything, would require a faster array processor, so the system at present is basically single-user for processing. For development and testing, the situation is quite different and the array processor is usually mostly idling; we are, therefore working on a scheme where the array processor will be available to several users on a multi-terminal system (eventually as a distributed system under DS1000) but to one user at a given time, and for a short period only (a few seconds or less).

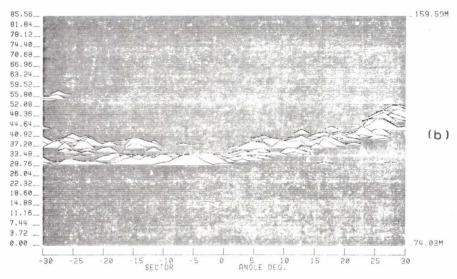

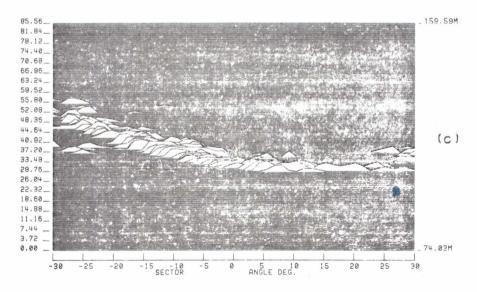

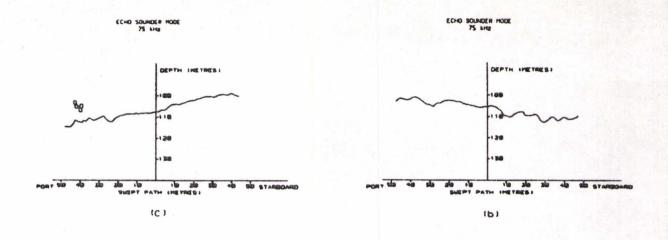

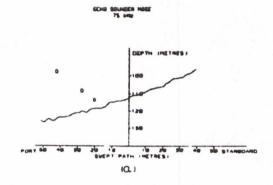

<u>D. Steiger</u> Please comment on the software used for the colour terminal — in particular the graphics and RTE driver.